# PB22H-KB System Module Hardware Reference Information

Order Number: EK-A0638-TD.001

14 July, 1993

This manual gives hardware reference information for the PB22H-KB system module.

**Revision Information:**

Final draft.

Digital Equipment Corporation Maynard, Massachusetts

#### Sign-off Draft, 14 July, 1993

Possession, use, or copying of the software described in this documentation is authorized only pursuant to a valid written license from Digital, an authorized, sublicensor, or the identified licensor.

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the interconnection of its products in the manner described in this document will not infringe existing or future patent rights, nor do the descriptions contained in this document imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1993.

All Rights Reserved.

The postpaid Reader's Comments forms at the end of this document request your critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation: Alpha AXP, AXP, DEC, DECchip, DECnet, Digital, OpenVMS, VAX DOCUMENT, and the DIGITAL logo.

$\operatorname{OSF}$  and  $\operatorname{OSF}/1$  are registered trademarks of the Open Software Foundation, Inc.

Microsoft is a registered trademark of Microsoft Corporation.

Windows NT is a trademark of Microsoft Corporation.

Intel is a registered trademark of Intel Corporation.

IBM, PS/2, and Personal Computer AT are registered trademarks of International Business Machines Corporation.

All other trademarks and registered trademarks are the property of their respective holders.

This document was prepared using VAX DOCUMENT, Version 2.1.

# Contents

| Preface | • • |  | • | •• | • | ••• | • |  | • | • | • • |  |  | • | • | • |  | • | • |  | • | • |  |  | • |  | • | • | • | • | • | • | • |  | • | • | • | • | • | • | • | • |  |  |  |  | х | ix |  |

|---------|-----|--|---|----|---|-----|---|--|---|---|-----|--|--|---|---|---|--|---|---|--|---|---|--|--|---|--|---|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|--|--|--|--|---|----|--|

|---------|-----|--|---|----|---|-----|---|--|---|---|-----|--|--|---|---|---|--|---|---|--|---|---|--|--|---|--|---|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|--|--|--|--|---|----|--|

# Part I System Module Overview

# 1 System Module Overview

| Overview                                  | 1–2  |

|-------------------------------------------|------|

| System Module Layout                      | 1–3  |

| Block Diagram                             | 1–4  |

| DECchip 21064 CPU                         | 1–5  |

| Summary                                   | 1–5  |

| DECchip 21064 CPU Features                | 1–5  |

| DECchip 21064 CPU Execution Units         | 1–7  |

| More Information                          | 1–7  |

| Intel 82350DT EISA Chip Set               | 1–8  |

| Intel 82358 EISA Bus Controller           | 1–8  |

| Intel 82357 Integrated System Peripheral  | 1–8  |

| Intel 82352 EISA Bus Buffer               | 1–9  |

| More Information                          | 1–9  |

| VLSI Technology VL82C106 Combination Chip | 1–10 |

| Real-Time Clock                           | 1–10 |

| Serial Lines                              | 1–10 |

| Line Printer Port                         | 1–11 |

| Parallel I/O                              | 1–11 |

| Keyboard and Mouse Ports                  | 1–11 |

| Periodic Interrupt Source                 | 1–12 |

| More Information                          | 1–12 |

# 2 Backup Cache

| Introduction                                | 2–1  |

|---------------------------------------------|------|

| In This Chapter                             | 2–1  |

| Backup Cache                                | 2–2  |

| Backup Cache organization                   | 2–3  |

| Control Store                               | 2–4  |

| Tag Store                                   | 2–5  |

| Data Store                                  | 2–6  |

| Cacheable and Noncacheable Memory Locations | 2–7  |

| Cacheable Memory Locations                  | 2–7  |

| Noncacheable Memory Locations               | 2–7  |

| Backup Cache Control                        | 2–8  |

| Backup Cache Address Translation            | 2–10 |

| Address Translation                         | 2–11 |

# 3 Lock Logic

| Introduction           | 3–1 |

|------------------------|-----|

| In This Chapter        | 3–1 |

|                        | 3–2 |

| Example                | 3–2 |

| Intel Code Example     | 3–3 |

| Alpha AXP Code Example | 3–3 |

# 4 System Module Memory

| Introduction              | 4–1 |

|---------------------------|-----|

| In This Chapter           | 4–1 |

| Memory Configurations     | 4–2 |

| Memory Sizes              | 4–2 |

| Configuring Memory        | 4–2 |

| Configuration Rules       | 4–2 |

| SIMM Socket Locations     | 4–3 |

| Memory Address Generation | 4–4 |

| Refreshing Memory         | 4–5 |

# 5 System Registers

| Introduction                    | 5–1 |

|---------------------------------|-----|

| In This Chapter                 | 5–1 |

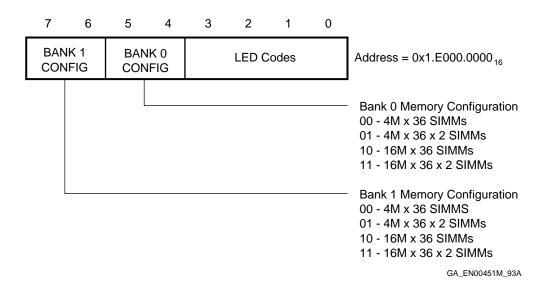

| System Control Register         | 5–2 |

| Description                     | 5–2 |

| Memory Configuration Bits       | 5–2 |

| LED Display Code Bits           | 5–3 |

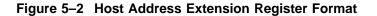

| Host Address Extension Register | 5–4 |

# 6 Exceptions and Interrupts

| Introduction                                           | 6–1  |

|--------------------------------------------------------|------|

| In This Chapter                                        | 6–1  |

| Exceptions and Interrupts                              | 6–2  |

| General Exceptions                                     | 6–3  |

| Machine Check Exceptions                               | 6–4  |

| Exception Handling                                     | 6–5  |

| PAL Priority Level                                     | 6–6  |

| PAL Code Entry 0020 <sub>16</sub>                      | 6–8  |

| PAL Code Entry 0020 <sub>16</sub> Characteristics      | 6–8  |

| PAL Code Entry 0020 <sub>16</sub> Parse Tree           | 6–8  |

| Machine Check Parse Tree                               | 6–9  |

| PAL Code Errors                                        | 6–10 |

| Parity Error During I_Cache or D_Cache Fill            | 6–10 |

| Interrupts                                             | 6–12 |

| Hardware Interrupts                                    | 6–12 |

| Interrupt Handling                                     | 6–13 |

| PAL Priority Levels                                    | 6–14 |

| PAL Code Entry 00E0 <sub>16</sub>                      | 6–15 |

| PAL Code Entry 00E016 Characteristics                  | 6–15 |

| Interrupt Parse Tree PAL code Entry 00E0 <sub>16</sub> | 6–16 |

| Hardware Interrupt Levels                              | 6–17 |

| Hardware 0 Interrupt                                   | 6–17 |

| Hardware 1 Interrupt                                   | 6–17 |

| Hardware 2 Interrupt                                   | 6–17 |

| Hardware 3 Interrupt                                   | 6–18 |

| Hardware 4 Interrupt                                   | 6–18 |

| Hardware 5 Interrupt                                   | 6–18 |

| Performance Counter X Interrupt                        | 6–18 |

| Asynchronous System Trap Interrupt                     | 6–18 |

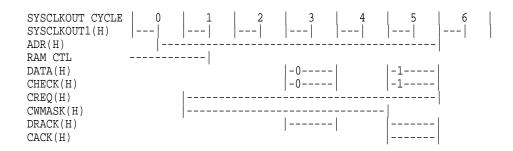

# 7 Direct Memory Access

| 7–1 |

|-----|

| 7–1 |

| 7–2 |

| 7–2 |

| 7–2 |

| 7–2 |

| 7–2 |

| 7–3 |

|     |

#### 8 Local Buses

| Introduction                               | 8–1 |

|--------------------------------------------|-----|

| In This Chapter                            | 8–1 |

| H_BUS                                      | 8–2 |

| H_BUS Description                          | 8–2 |

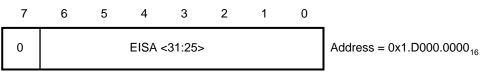

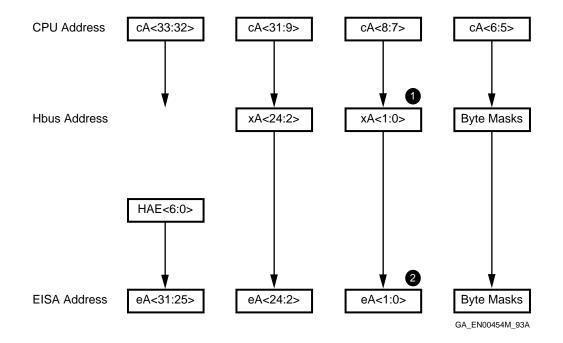

| DECchip 21064 CPU Cycle Mapping            | 8–2 |

| DECchip 21064 CPU Address Translation      | 8–3 |

| Example H_BUS and EISA Address Translation | 8–6 |

| L_BUS                                      | 8–8 |

| Peripheral Selection                       | 8–8 |

# 9 Error Handling

| Introduction                               | 9–1 |

|--------------------------------------------|-----|

|                                            | • • |

| In This Chapter                            | 9–1 |

| Error Handling Overview                    | 9–2 |

| I/O Error Detection                        | 9–3 |

| Parity Error Detection                     | 9–4 |

| I_Stream Parity Error Flow                 | 9–4 |

| D_Stream Parity Error Flow                 | 9–5 |

| Backup Cache Parity Errors                 | 9–6 |

| Backup Cache Data Parity Errors            | 9–6 |

| Backup Cache Tag and Control Parity Errors | 9–6 |

| Tag Address Parity Error Flow              | 9–6 |

| Tag Control Parity Error Flow              | 9–6 |

| Nonmaskable Interrupt Errors               | 9–8 |

| NMI Error Types                            | 9–8 |

| NMI Error Handling                         | 9–9 |

| NMI Error IDs                              | 9–9 |

#### 10 Power-Up Initialization

| Introduction                                    | 10–1  |

|-------------------------------------------------|-------|

| In This Chapter                                 | 10–1  |

| Power-Up Initialization Overview                | 10–2  |

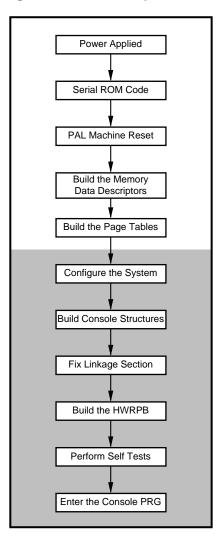

| Power-Up Initialization Flow                    | 10–3  |

| Power-Up Diagnostics                            | 10–5  |

| Power-Up Initialization Routines                | 10–7  |

| SROM\$POWERUP                                   | 10–7  |

| SROM\$SIZE _MEMORY                              | 10–8  |

| SROM\$MEM_TEST                                  | 10–8  |

| SROM\$SYSROM _LOAD                              | 10–8  |

| SROM\$MEM_FILL                                  | 10–8  |

| SROM\$MEM _RDCMP                                | 10–9  |

| SROM\$MEM_PACKROM                               | 10–10 |

| SROM\$DIAG_REPORT                               | 10–11 |

| SROM\$CONSOLE                                   | 10–11 |

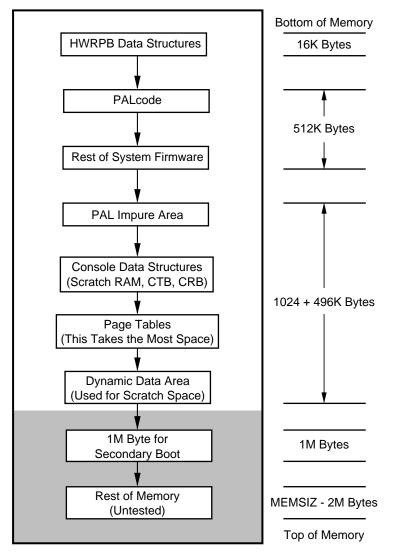

| Map of Memory Following Power-Up Initialization | 10–12 |

|                                                 |       |

# Part II DECchip 21064 CPU Overview

# 11 Alpha AXP Architecture

| Introduction                          | 11–1  |

|---------------------------------------|-------|

| In This Chapter                       | 11–1  |

| AXP Addressing and Data Types         | 11–2  |

| Addressing                            | 11–2  |

| Data types and Floating Point Formats | 11–2  |

| Byte and Word Data Types              | 11–3  |

| Byte                                  | 11–3  |

| Word                                  | 11–3  |

| Longword and Quadword Data Type       | 11–4  |

| Longword                              | 11–4  |

| Quadword                              | 11–4  |

| Longword Data Format                  | 11–5  |

| Longword Data Format                  | 11–5  |

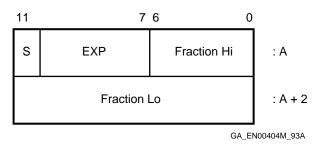

| F_Floating Floating Point Format      | 11–6  |

| F_Floating                            | 11–6  |

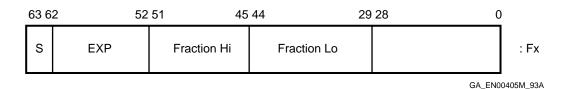

| G_Floating Floating Point Format      | 11–8  |

| G_Floating                            | 11–8  |

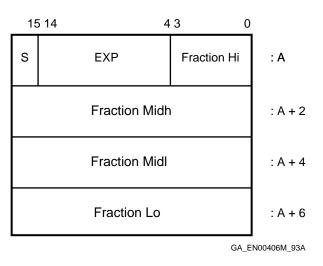

| D_Floating Floating Point Format      | 11–10 |

| D_Floating                            | 11–10 |

| S_Floating Floating Point Format      | 11–12 |

|                                       |       |

| S_Floating                          | 11–12 |

|-------------------------------------|-------|

| Other Data Type Information         | 11–15 |

| Data Types with No Hardware Support | 11–15 |

| Data Type Performance Penalties     | 11–15 |

| Alpha AXP Registers                 | 11–16 |

| Program Counter Register            | 11–16 |

| Processor Status Register           | 11–16 |

| Integer Registers                   | 11–16 |

| Floating-Point Registers            | 11–17 |

| Lock Registers                      | 11–18 |

| Internal Processor Registers        | 11–18 |

| Alpha AXP Instruction Formats       | 11–19 |

# 12 I-Box Internal Processor Registers

| Introduction                            | 12–1  |

|-----------------------------------------|-------|

| In This Chapter                         | 12–1  |

| I-Box Functions                         | 12–2  |

| TB_TAG Register                         | 12–3  |

| ITB_PTE Register                        | 12–4  |

| ITB_PTE_TEMP and Other ITB Registers    | 12–6  |

| ITB_ZAP Register                        | 12–7  |

| ITB_ASM Register                        | 12–7  |

| ITB_IS Register                         | 12–7  |

| ICCSR Register                          | 12–8  |

| ICCSR Register Fields                   | 12–9  |

| BHE and BPE Branch Prediction Selection | 12–10 |

| Performance Counters                    | 12–11 |

| Performance Counter 0                   | 12–12 |

| Performance Counter 2                   | 12–13 |

| EXC_ADDR Register                       | 12–14 |

| EXC_ADDR Format                         | 12–15 |

| EXC_SUM Register                        | 12–16 |

| SL_CLR Register                         | 12–18 |

| SL_CLR Format                           | 12–18 |

| SL_CLR Fields                           | 12–18 |

| SL_RCV Register                         | 12–19 |

| SL_RCV Format                           | 12–19 |

| SL_XMIT Register                        | 12–20 |

| Processor Status Register               | 12–21 |

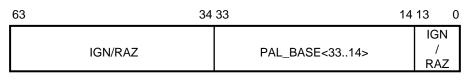

| PAL_BASE Register                       | 12–22 |

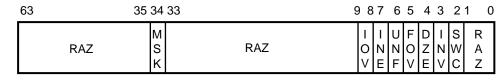

| HIRR Register                           | 12–23 |

| SIRR Register                           | 12–25 |

| ASTRR Register | 12–26 |

|----------------|-------|

| HIER Register  |       |

| SIER Register  | 12–29 |

| ASTER Register | 12–30 |

# 13 A-Box Internal Processor Registers

| Introduction             | 13–1  |

|--------------------------|-------|

| In This Chapter          | 13–1  |

| A-BOX Sections           | 13–2  |

| TB_CTL Register          | 13–3  |

| DTB_PTE Register         | 13–4  |

| DTB_PTE_TEMP Register    | 13–6  |

| MM_CSR Register          | 13–7  |

| ABOX_CTL Register        | 13–8  |

| ALT_MODE Register        | 13–11 |

| Cycle Counter Registers  | 13–12 |

| CC Register              | 13–12 |

| CC_CTL Register          | 13–12 |

| BIU_CTL Register         | 13–13 |

| Other A-BOX Registers    | 13–19 |

| Virtual Address Register | 13–19 |

| DTB_ZAP Register         | 13–19 |

| DTB_ASM Register         | 13–19 |

|                          |       |

# 14 PAL Temporary Registers

| Introduction           | 14–1  |

|------------------------|-------|

| In This Chapter        | 14–1  |

| BIU_STAT Register      |       |

| DC_STAT Register       |       |

| BIU_ADDR Register      | 14–8  |

| DC_ADDR Register       | 14–9  |

| FILL_ADDR Register     | 14–10 |

| FILL_SYNDROME Register | 14–11 |

| BC_TAG Register        | 14–12 |

|                        |       |

# 15 CPU Cycle Types, Transactions, and Initialization

| Introduction                              | 15–1  |

|-------------------------------------------|-------|

| In This Chapter                           | 15–1  |

| DECchip 21064 CPU Cycle Types             | 15–2  |

| DECchip 21064 CPU Transactions            | 15–5  |

| Fast External Cache Read Hit Transaction  | 15–6  |

| Example                                   | 15–6  |

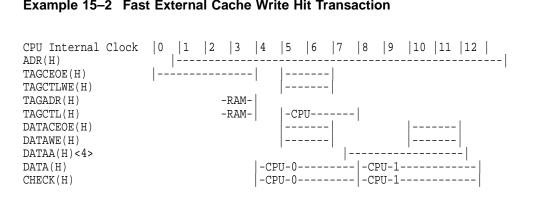

| Fast External Cache Write Hit Transaction | 15–7  |

| Example                                   | 15–7  |

| READ_BLOCK Transaction                    | 15–8  |

| Example                                   | 15–9  |

| WRITE_BLOCK Transaction                   | 15–10 |

| Example                                   | 15–11 |

| LDxL and STxC Transactions                | 15–12 |

| LDxL Transaction                          | 15–12 |

| StxC Transaction                          | 15–12 |

| BARRIER Transaction                       | 15–13 |

| Example                                   | 15–13 |

| FETCH and FETCHM Transactions             | 15–14 |

| FETCHM Transaction                        | 15–14 |

| Example                                   | 15–15 |

| FETCHM Transaction                        | 15–15 |

| Initialization                            | 15–16 |

|                                           |       |

# Part III Intel 82357 Integrated System peripheral Chip Functions

#### 16 DMA Controller

| Introduction                              | 16–1 |

|-------------------------------------------|------|

| In This Chapter                           | 16–1 |

| Overview                                  | 16–3 |

| Programmable Channels                     | 16–3 |

| DMA Controller Device Sizes and ISA Modes | 16–3 |

| DMA Controller Transfer Modes             | 16–3 |

| Additional DMA Controller Functions       | 16–4 |

| DMA Controller Master and Slave Modes     | 16–4 |

| DMA Controller Transfer Modes             | 16–5 |

| Single Transfer Mode                      | 16–5 |

| Block Transfer Mode                       | 16–5 |

| Demand Transfer Mode                      | 16–6 |

| Cascade Mode                              | 16–6 |

| DMA Transfer Types                                       | 16–7  |

|----------------------------------------------------------|-------|

| Read Transfer                                            | 16–7  |

| Write Transfer                                           | 16–7  |

| Verify Transfer                                          | 16–7  |

| Autoinitialization                                       | 16–8  |

| Master and Slave Modes                                   | 16–9  |

| DMA Controller Registers                                 | 16–10 |

| Stop Registers                                           | 16–11 |

| DMA Controller Memory Low-Page Register                  | 16–13 |

| DMA Controller Memory High-Page Register                 | 16–14 |

| Address Compatibility Mode                               | 16–15 |

| Current Address Register                                 | 16–16 |

| Address Shifting When Programmed for 16-Bit I/O Count by |       |

| Words                                                    | 16–16 |

| Current Word Register                                    | 16–17 |

| Base Page, Base Address, and Base Word Count Registers   | 16–18 |

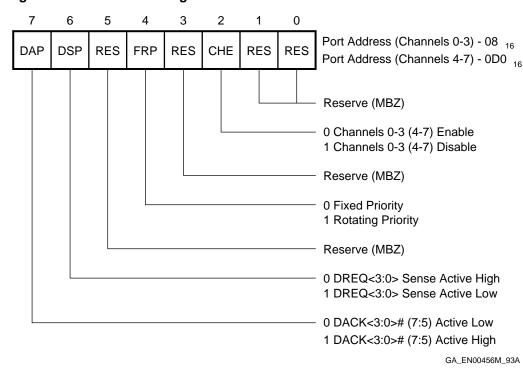

| Command Register                                         | 16–19 |

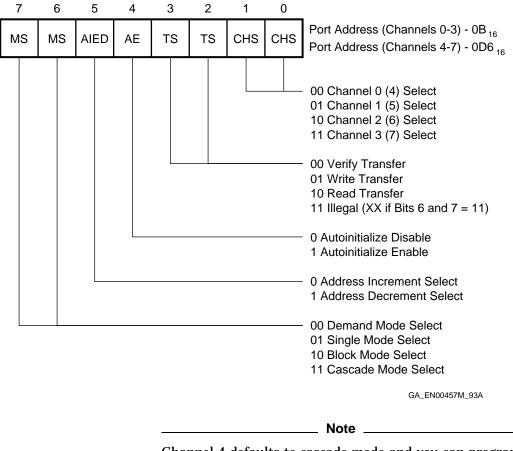

| Mode Register                                            | 16–20 |

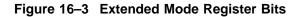

| Extended Mode Registers                                  | 16–22 |

| 8-Bit I/O Count by Bytes Mode                            | 16–23 |

| 16 Bit I/O Count by Words Mode                           | 16–24 |

| 16 Bit I/O Count by Bytes Mode                           | 16–24 |

| 32 Bit I/O Count by Bytes Mode                           | 16–24 |

| EOP Input or Output Selection                            | 16–25 |

| Stop Register Selection                                  | 16–25 |

| Summary of DMA Transfer Sizes                            | 16–25 |

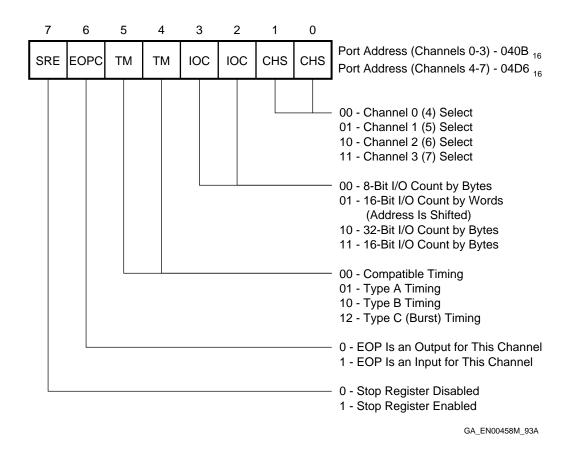

| Request Register                                         | 16–26 |

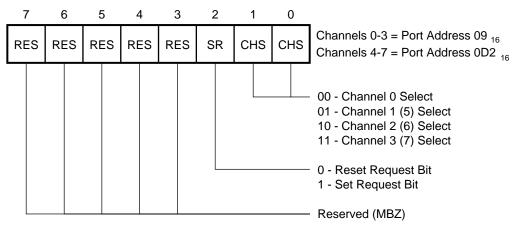

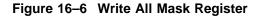

| Mask Register                                            | 16–27 |

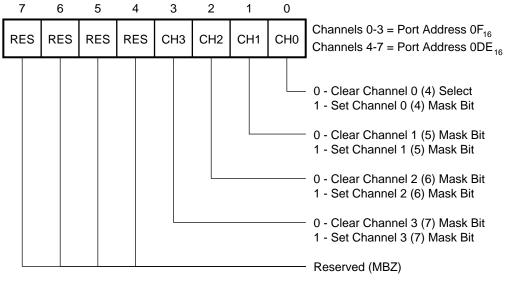

| DMA Controller Status Register                           | 16–29 |

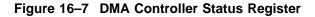

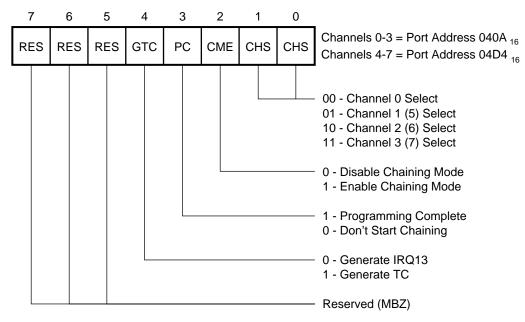

| Set Chaining Mode Register                               | 16–31 |

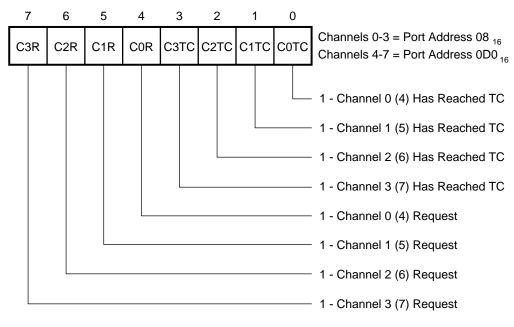

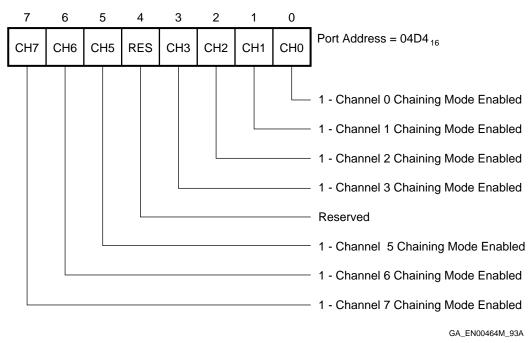

| Set Chaining Mode Status Register                        | 16–33 |

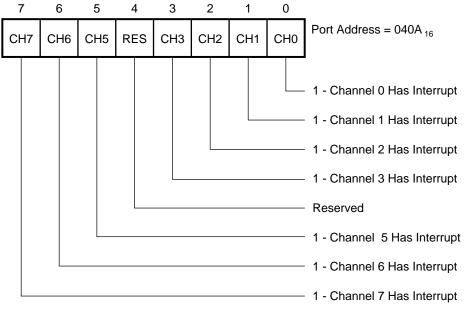

| Channel Interrupt Status Register                        | 16–34 |

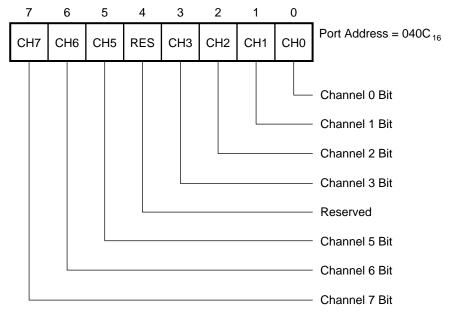

| Chain Buffer Expiration Control Register                 | 16–35 |

| DMA Controller Software Commands                         | 16–36 |

| Clear Byte Pointer Flip-Flop Command                     | 16–36 |

| Master Clear Command                                     | 16–36 |

| Clear Mask Register Command                              | 16–37 |

| Terminal Count and EOP Summary                           | 16–38 |

| Example                                                  | 16–38 |

| EISA Bus Master Status Latch                             | 16–40 |

# 17 Interrupt Controller

| Introduction                                       | 17–1  |

|----------------------------------------------------|-------|

| In This Chapter                                    | 17–1  |

| Interrupt Controller Overview                      | 17–3  |

| Interrupt Controller I/O Address Map               | 17–4  |

| Interrupt Assignments                              | 17–5  |

| Interrupt Details and Registers                    | 17–7  |

| Interrupt Request Register and In-Service Register | 17–7  |

| Priority Resolver                                  | 17–7  |

| Interrupt Mask Register                            | 17–7  |

| Interrupt (INT)                                    | 17–7  |

| Interrupt Acknowledge (INTA)                       | 17–7  |

| Interrupt Sequence                                 | 17–8  |

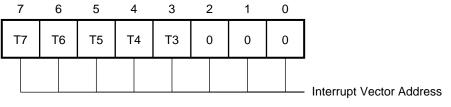

| 80x86 Mode                                         | 17–9  |

| Programming the Interrupt Controller               | 17–10 |

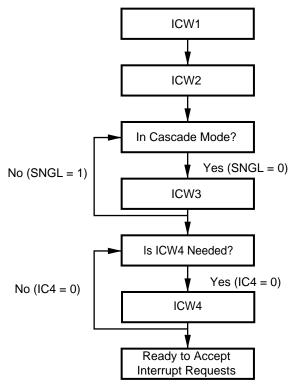

| Initialization Command Words                       | 17–11 |

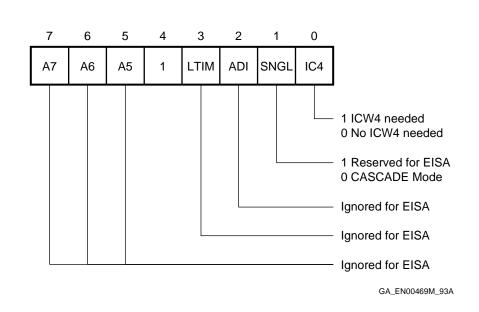

| Initialization Command Words 1 and 2               | 17–13 |

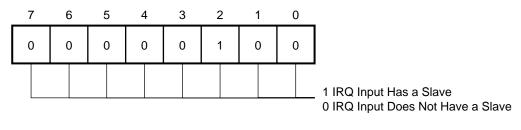

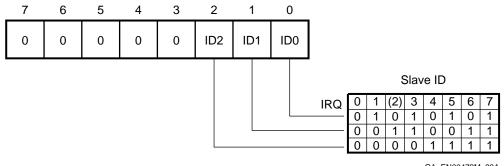

| Initialization Command Word 3 (ICW3)               | 17–15 |

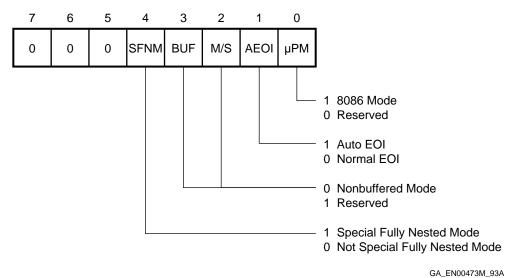

| Initialization Command Word 4 (ICW4)               | 17–16 |

| Operation Control Words                            | 17–17 |

| Operation Command Words                            | 17–17 |

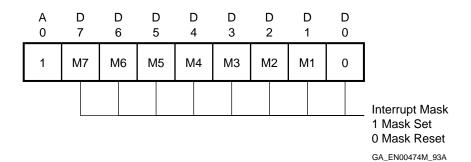

| Operation Command Word 1 (OCW1)                    | 17–19 |

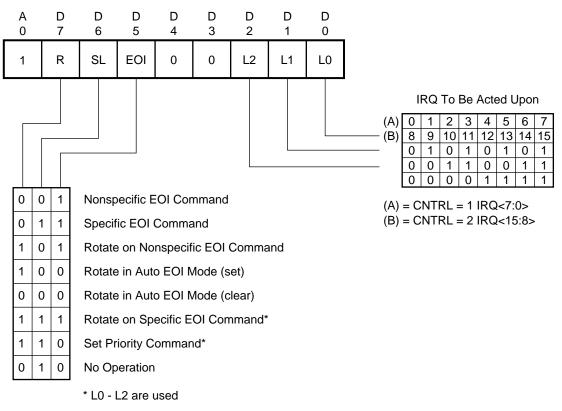

| Operation Command Word 2 (OCW2)                    | 17–20 |

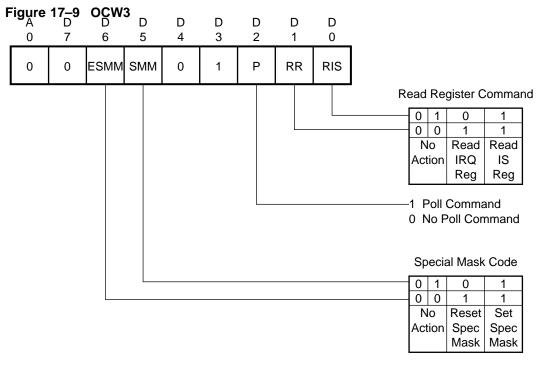

| Operation Command Word 3 (OCW3)                    | 17–21 |

| End of Interrupt Operation                         | 17–22 |

| End of Interrupt (EOI)                             | 17–22 |

| Automatic End of Interrupt (AEOI)                  | 17–23 |

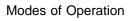

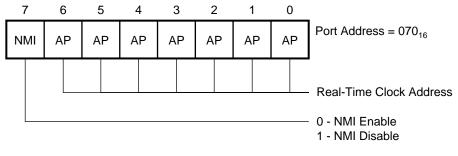

| Modes of Operation                                 | 17–24 |

| Fully Nested Mode                                  | 17–24 |

| Special Fully Nested Mode                          | 17–25 |

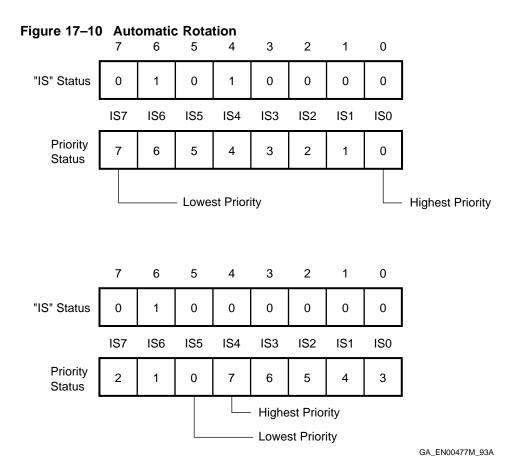

| Automatic Rotation (Equal Priority Devices)        | 17–26 |

| Specific Rotation (Specific Priority)              | 17–27 |

| Poll Command                                       | 17–27 |

| Cascade Mode                                       | 17–28 |

| Edge- and Level-Triggered Modes                    | 17–28 |

| Edge and Level-Triggered Control Register          | 17–29 |

| Interrupt Masks                                    | 17–31 |

| Masking on an Individual Interrupt Request Basis   | 17–31 |

| Special Mask Mode                                  | 17–31 |

| Reading the Interrupt Controller Status            | 17–32 |

|                                                    |       |

#### 18 Nonmaskable Interrupt Ports

| Introduction                                       | 18–1  |

|----------------------------------------------------|-------|

| In This Chapter                                    | 18–1  |

| Overview                                           | 18–2  |

| Causes of Nonmaskable Interrupts                   | 18–2  |

| Nonmaskable Interrupt Registers                    | 18–3  |

| Nonmaskable Interrupt Service Routines             | 18–4  |

| NMI Status and Control Register                    | 18–5  |

| NMI Extended Status and Control Register           | 18–7  |

| 82357 B-Stepping                                   | 18–8  |

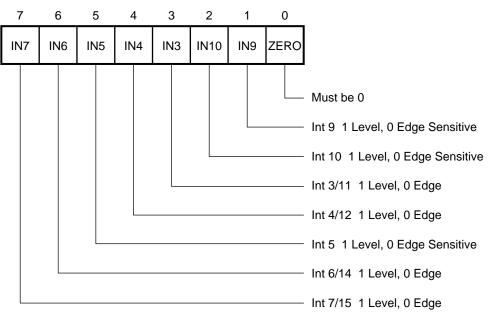

| Software NMI Generation                            | 18–9  |

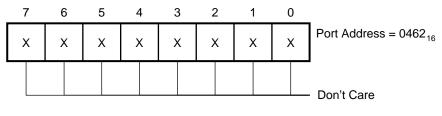

| NMI Enable and Disable and Real-Time Clock Address | 18–10 |

#### 19 Interval Timer

| Introduction                         | 19–1 |

|--------------------------------------|------|

| In This Chapter                      | 19–1 |

| Interval Timer Overview              | 19–2 |

| Interval Timer                       | 19–2 |

| Timer Frequencies                    | 19–2 |

| Timer 1 Functions                    | 19–2 |

| Timer 2 Functions                    | 19–3 |

| Programming the Interval Timer       | 19–4 |

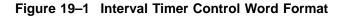

| Interval Timer Control Word Format   | 19–6 |

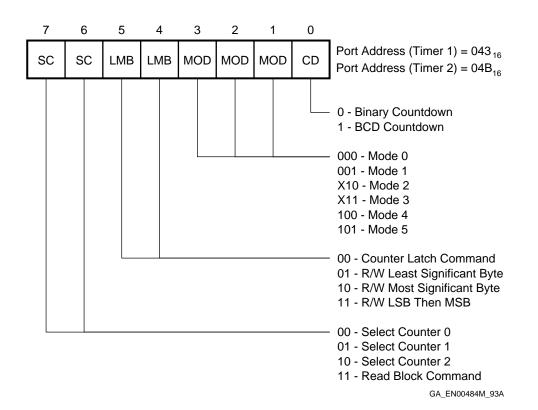

| Interval Timer Counter Latch Command | 19–8 |

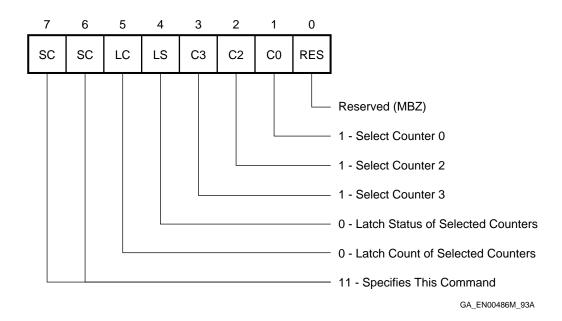

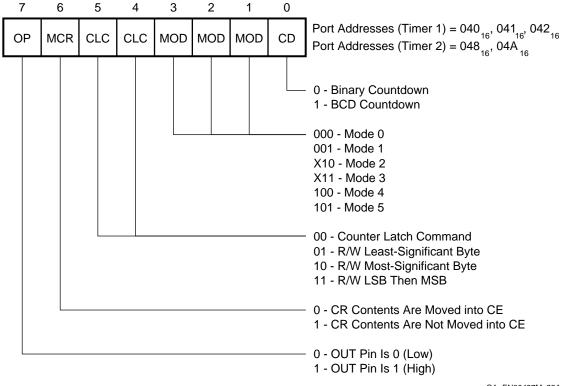

| Interval Timer Read Back Command     | 19–9 |

|                                      |      |

#### Part IV VLSI Technology VL82C106 Combination Chip Functions

#### 20 Serial Communications Ports

| Introduction                          | 20–1  |

|---------------------------------------|-------|

| In This Chapter                       | 20–1  |

| Serial Communications Port Overview   | 20–2  |

| Asynchronous Communications Registers | 20–3  |

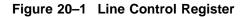

| Line Control Registers                | 20–5  |

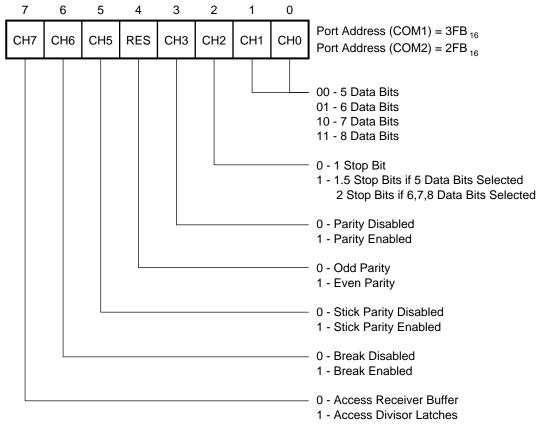

| Line Status Registers                 | 20–7  |

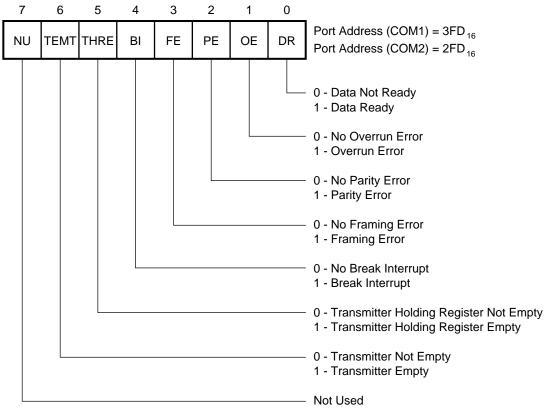

| Modem Control Registers               | 20–11 |

| Modem Status Registers                | 20–13 |

| Divisor Latches                       | 20–16 |

| Receive Buffer Registers              | 20–17 |

|                                       |       |

| Transmitter Holding Registers and Scratchpad Registers | 20–18 |

|--------------------------------------------------------|-------|

| Transmitter Holding Registers                          | 20–18 |

| Scratchpad Registers                                   | 20–18 |

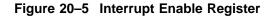

| Interrupt Identification Registers                     | 20–19 |

| Interrupt Enable Registers                             | 20–20 |

| Serial Transmission Process                            | 20–21 |

| Serial Reception Process                               | 20–22 |

| Baud Rate Generator                                    | 20–23 |

| Master Reset                                           | 20–27 |

| Programming the Serial Channels                        | 20–29 |

| Software Reset of the Serial Channels                  | 20–29 |

#### 21 Line Printer Port

| Introduction                                    | 21–1 |

|-------------------------------------------------|------|

| In This Chapter                                 | 21–1 |

| Line printer Port Overview                      | 21–2 |

| Line Printer Port Data Register (Register 0)    | 21–3 |

| Compatibility Mode                              | 21–3 |

| Extended Mode                                   | 21–3 |

| Line Printer Port Status Register (Register 1)  | 21–4 |

| Line Printer Port Control Register (Register 2) | 21–6 |

#### 22 Real-Time Clock

| Introduction                        | 22–1  |

|-------------------------------------|-------|

| In This Chapter                     | 22–1  |

| RTC Overview                        | 22–2  |

| RTC Programmer's Model              | 22–3  |

| Time of Day Registers               | 22–5  |

| RTC Control Registers               | 22–6  |

| RTC Control Register A              | 22–7  |

| Rate-Selection Bits                 | 22–7  |

| Divisor-Selection Bits              | 22–9  |

| Update in Progress Bit              | 22–9  |

| RTC Control Register B              | 22–10 |

| Daylight Savings Enable Bit         | 22–10 |

| 24/12 Control Bit                   | 22–10 |

| Data Mode Bit                       | 22–11 |

| Bit 3                               | 22–11 |

| RTC Update End Interrupt Enable Bit | 22–11 |

| RTC Alarm Interrupt Enable Bit      | 22–11 |

| RTC Periodic Interrupt Enable Bit   | 22–11 |

| Set Command Bit                        | 22–11 |

|----------------------------------------|-------|

| RTC Control Register C                 | 22–12 |

| Bits 0 to 3                            | 22–12 |

| RTC Update Ended Interrupt Flag Bit    | 22–12 |

| RTC Alarm Interrupt Flag Bit           | 22–12 |

| RTC Periodic Interrupt Flag Bit        | 22–13 |

| RTC Interrupt Request Pending Flag Bit | 22–13 |

| RTC Control Register D                 | 22–14 |

| Bits 0 to 6                            | 22–14 |

| Valid RAM Data and Time Bit            | 22–14 |

| General RTC Notes                      | 22–15 |

| Set Operation                          | 22–15 |

| BCD Versus Binary                      | 22–15 |

| RTC Update Operation                   | 22–15 |

| RTC Alarm Operation                    | 22–15 |

| RTC Interrupts                         | 22–16 |

| Divider Control                        | 22–16 |

| RTC Periodic Interrupt Selection       | 22–17 |

| RTC Update Cycle                       | 22–17 |

|                                        |       |

# 23 Keyboard Controller

| PS/2 Command Set and Conversion Code23–2Keyboard Serial I/O23–2User RAM23–2Keyboard Parallel Ports23–2Port 60 <sub>16</sub> and Status Register Support23–2Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6 | Introduction                                      | 23–1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|

| PS/2 Command Set and Conversion Code23–2Keyboard Serial I/O23–2User RAM23–2Keyboard Parallel Ports23–2Port 60 <sub>16</sub> and Status Register Support23–2Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6 | In This Chapter                                   | 23–1 |

| Keyboard Serial I/O23–2User RAM23–2Keyboard Parallel Ports23–2Port 60 <sub>16</sub> and Status Register Support23–2Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6                                         | Keyboard Controller Overview                      | 23–2 |

| User RAM23–2Keyboard Parallel Ports23–2Port 60 <sub>16</sub> and Status Register Support23–2Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6                                                                | PS/2 Command Set and Conversion Code              | 23–2 |

| User RAM23–2Keyboard Parallel Ports23–2Port 60 <sub>16</sub> and Status Register Support23–2Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6                                                                | Keyboard Serial I/O                               | 23–2 |

| Port 6016 and Status Register Support23–2Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6                                                                                                                   |                                                   | 23–2 |

| Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6                                                                                                                                                            | Keyboard Parallel Ports                           | 23–2 |

| Keyboard Port Interface Protocol23–3Keyboard Controller Programmer Interface23–4PS/2 Mode Register23–5PS/2 Status Register23–6                                                                                                                                                            | Port 60 <sub>16</sub> and Status Register Support | 23–2 |

| PS/2 Mode Register         23–5           PS/2 Status Register         23–6                                                                                                                                                                                                               | Keyboard Port Interface Protocol                  | 23–3 |

| PS/2 Status Register                                                                                                                                                                                                                                                                      | Keyboard Controller Programmer Interface          | 23–4 |

|                                                                                                                                                                                                                                                                                           | PS/2 Mode Register                                | 23–5 |

| Keyboard Controller Command Set 23–8                                                                                                                                                                                                                                                      | PS/2 Status Register                              | 23–6 |

|                                                                                                                                                                                                                                                                                           | Keyboard Controller Command Set                   | 23–8 |

# 24 Chip Select Registers

| Introduction                                             | 24–1  |

|----------------------------------------------------------|-------|

| In This Chapter                                          | 24–1  |

| Chip Select Registers Overview                           | 24–2  |

| Chip Select Base Address Register (LSB) Bit Descriptions | 24–3  |

| Chip Select Base Address Register (MSB) Bit Descriptions | 24–4  |

| Chip Select Range Register Bit Descriptions              | 24–5  |

| Chip Select Range Register Bits 0-4                      | 24–5  |

| Chip Select Range Register Bits 5 and 6                  | 24–5  |

| Chip Select Range Register Bit 7                         | 24–6  |

| Default Chip Selects                                     | 24–7  |

| Chip Control Registers                                   | 24–8  |

| Control Register 0                                       | 24–9  |

| System Board Enable Control Bit                          | 24–9  |

| Communications Port 1 Enable Control Bit                 | 24–9  |

| Communications Port 1 Default Address Control Bit        | 24–10 |

| Line Printer Port Enable Control Bit                     | 24–10 |

| Line Printer Port Default 0 and 1 Control Bits           | 24–10 |

| Line Printer Extended Mode Control Bit                   | 24–10 |

| Control Register 1                                       | 24–11 |

| Communications Port 2 Enable Bit                         | 24–11 |

| PC/AT or PS/2 Compatible Keyboard Bit                    | 24–11 |

| Private Controls Enable Bit                              | 24–12 |

| Chip Select Decode Mode Bit                              | 24–12 |

| Bits 4-7                                                 | 24–12 |

|                                                          |       |

#### Part V Appendixes

# A System I/O Map

| Introduction                                | A–1  |

|---------------------------------------------|------|

| In This Appendix                            | A–1  |

| System I/O Map                              | A–2  |

| ISA Expansion Address Aliases for 0100–03FF |      |

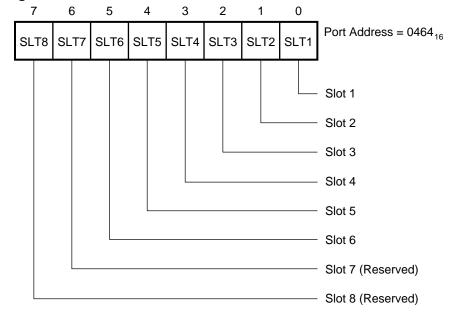

| EISA Slot-Specific Addresses                | A–13 |

# **B** Connector Pin Specifications

| Introduction                                    | B–1  |

|-------------------------------------------------|------|

| In This Appendix                                | B–1  |

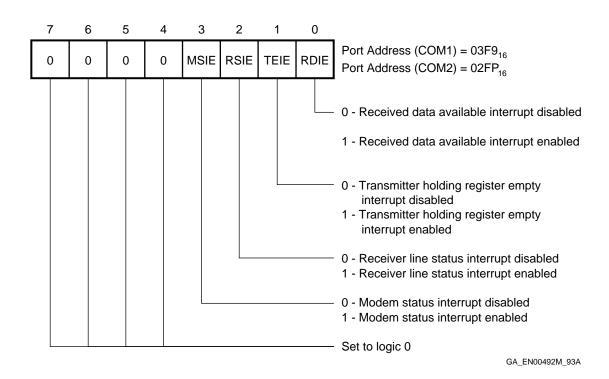

| Internal Connector Locations                    | B–2  |

| Power Connectors J22 and J23                    | B–3  |

| J22                                             | B–3  |

| J23                                             | B–3  |

| J22 and J23 Pin Specifications                  | B–3  |

| Battery Power Connector (J25)                   | B–4  |

| Battery Power Connector (J25)                   | B–4  |

| Front Panel Connector (J24)                     | B–5  |

| Front Panel Connector (J24)                     | B–5  |

| Auxiliary Fan Power Connector (J8)              | B–6  |

| Auxiliary Fan Power Connector (J8)              | B–6  |

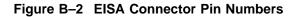

| EISA Connector Pin Specifications               | B–7  |

| EISA Connectors                                 | B–7  |

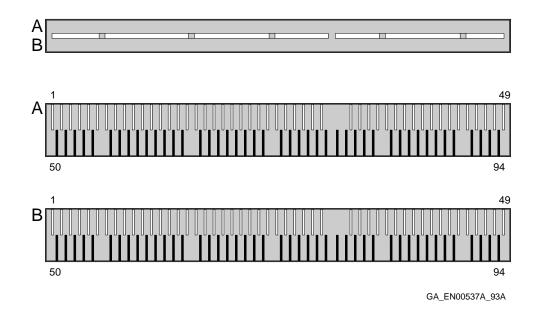

| Keyboard and Mouse Connector Pin Specifications | B–10 |

| Summary                                         | B–10 |

| Keyboard and Mouse Connector Illustration       | B–10 |

| Keyboard and Mouse Connector Pin Specifications | B–10 |

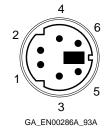

| Serial Port Pin Specifications                  | B–11 |

| Summary                                         | B–11 |

| Serial Port Illustration                        | B–11 |

| Serial Port Pin Specifications                  | B–11 |

| Parallel Port Pin Specifications                | B–12 |

| Summary                                         | B–12 |

| Parallel Port Illustration                      | B–12 |

| Parallel Port Pin Specifications                | B–12 |

|                                                 |      |

#### Glossary

Index

# Examples

| 3–1  | Intel Lock Logic Code Fragment            | 3–3   |

|------|-------------------------------------------|-------|

| 3–2  | Alpha AXP Lock Logic Code Fragment        | 3–3   |

| 12–1 | Exception Address Code                    | 12–15 |

| 15–1 | Fast External Cache Read Hit Transaction  | 15–6  |

| 15–2 | Fast External Cache Write Hit Transaction | 15–7  |

| 15–3 | READ_BLOCK Transaction                    | 15–9  |

| 15–4 | WRITE_BLOCK Transaction                   | 15–11 |

| 15–5 | BARRIER Transaction                       | 15–13 |

| 15–6 | FETCH Transaction                         | 15–15 |

|      |                                           |       |

# Figures

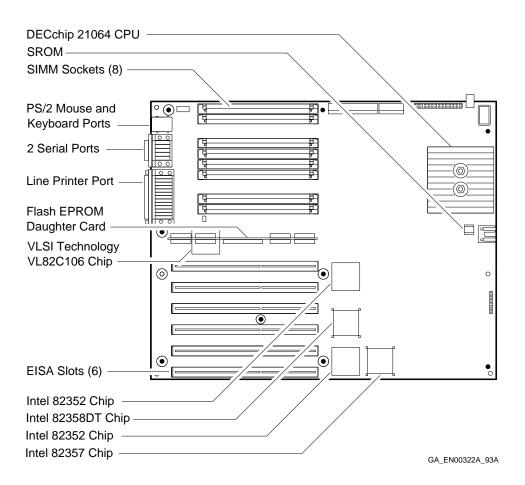

| 1–1  | Component Layout                                | 1–3   |

|------|-------------------------------------------------|-------|

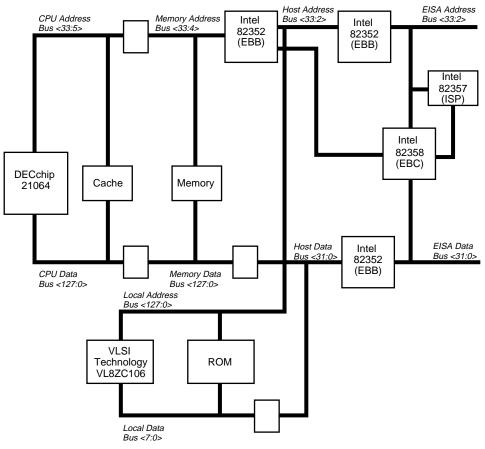

| 1–2  | PB22H-KB System Module Block Diagram            | 1–4   |

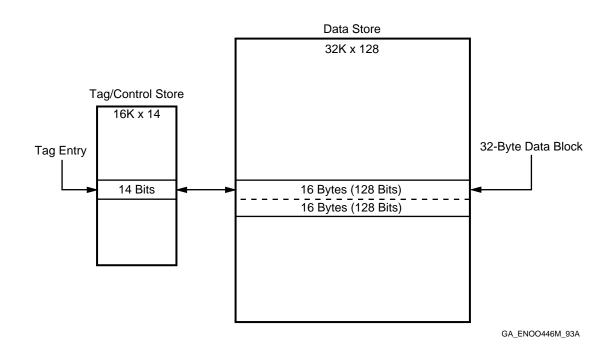

| 2–1  | Backup Cache Organization                       | 2–3   |

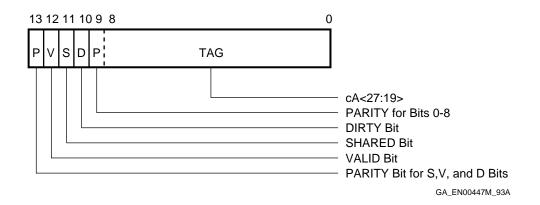

| 2–2  | Backup Cache Entry Tag and Control Bits         | 2–5   |

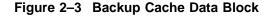

| 2–3  | Backup Cache Data Block                         | 2–6   |

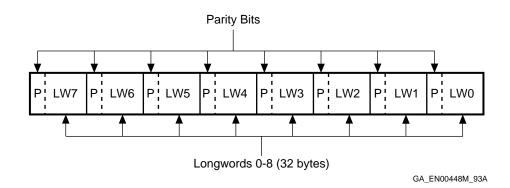

| 2–4  | Backup Cache Address Translation                | 2–11  |

| 4–1  | SIMM Socket Locations                           | 4–3   |

| 5–1  | System Control Register                         | 5–2   |

| 5–2  | Host Address Extension Register Format          | 5–4   |

| 6–1  | Machine Check Exception Parse Tree              | 6–9   |

| 6–2  | Interrupt Parse Tree                            | 6–16  |

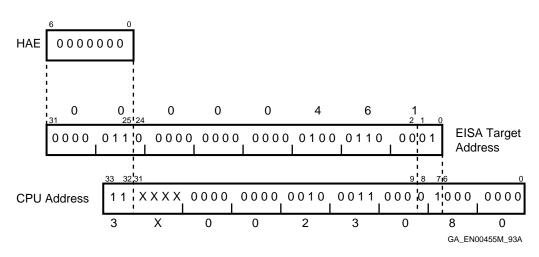

| 8–1  | H_BUS and EISA Bus Address Translation          | 8–6   |

| 8–2  | CA and EISA Bus Address Translation             | 8–7   |

| 10–1 | Power-Up Initialization Flow                    | 10–4  |

| 10–2 | Map of Memory Following Power-Up Initialization | 10–13 |

| 11–1 | Byte Data Format                                | 11–3  |

| 11–2 | Word Data Format                                | 11–3  |

| 11–3 | Longword Data Format                            | 11–5  |

| 11–4 | Quadword Data Format                            | 11–5  |

| 11–5 | F_Floating Data Format                          | 11–6  |

| 11–6 | F_Floating Register                             | 11–6  |

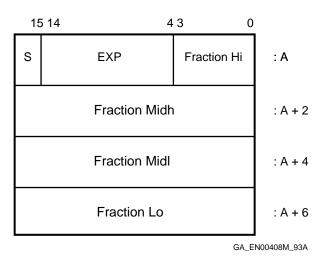

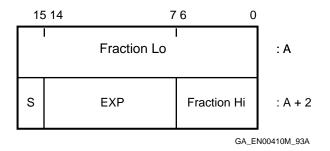

| 11–7 | G_Floating Operand                              | 11–8  |

| 11–8 | G_Floating Data Format                          | 11–8  |

|      |                                                 |       |

| 11–9  | D_Floating Data Format           | 11–10 |

|-------|----------------------------------|-------|

| 11–10 | D_Floating Register Format       | 11–10 |

| 11–11 | S_Floating Operand               | 11–12 |

| 11–12 | S_Floating Register Format       | 11–12 |

| 12–1  | TB_TAG Register Format           | 12–3  |

| 12–2  | ITB_PTE Register Format          | 12–5  |

| 12–3  | ITB_PTE_TEMP Register Format     | 12–6  |

| 12–4  | ICCSR Register Format            | 12–8  |

| 12–5  | EXC_ADDR Register Format         | 12–15 |

| 12–6  | EXC_SUM Register Format          | 12–16 |

| 12–7  | SL_CLR Register Format           | 12–18 |

| 12–8  | SL_RCV Register Format           | 12–19 |

| 12–9  | SL_XMIT Register Format          | 12–20 |

| 12–10 | Processor Status Register Format | 12–21 |

| 12–11 | PAL_BASE Register Format         | 12–22 |

| 12–12 | HIRR Register Format             | 12–23 |

| 12–13 | SIRR Register Format             | 12–25 |

| 12–14 | ASTRR Register Format            | 12–27 |

| 12–15 | HIER Register Format             | 12–28 |

| 12–16 | SIER Register Format             | 12–29 |

| 12–17 | ASTER Register Format            | 12–30 |

| 13–1  | TB_CTL Register Format           | 13–3  |

| 13–2  | DTB_PTE Register Format          | 13–5  |

| 13–3  | DTB_PTE_TEMP Register Format     | 13–6  |

| 13–4  | MM_CSR Register Format           | 13–7  |

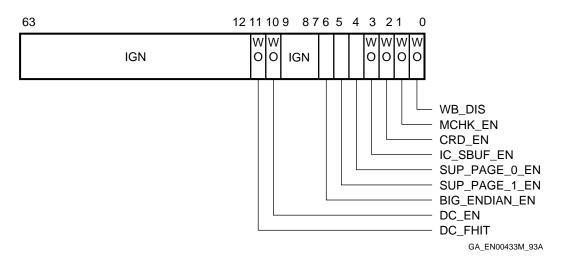

| 13–5  | ABOX_CTL Register Format         | 13–8  |

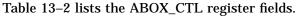

| 13–6  | ALT_MODE Register Format         | 13–11 |

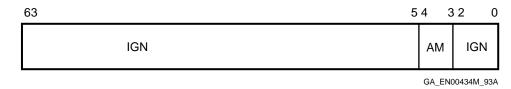

| 13–7  | BIU_CTL Register Format          | 13–13 |

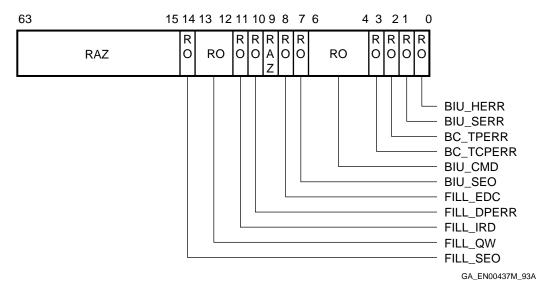

| 14–1  | BIU_STAT Register Format         | 14–3  |

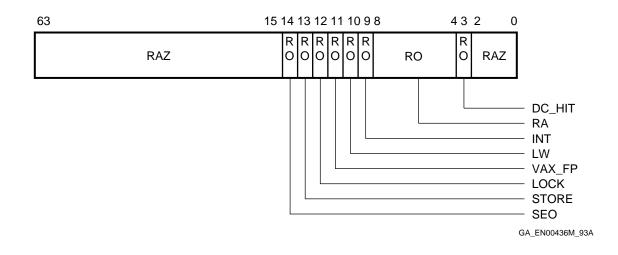

| 14–2  | DC_STAT Register Format          | 14–6  |

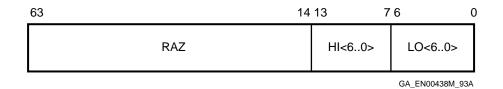

| 14–3  | FILL_SYNDROME Register Format    | 14–11 |

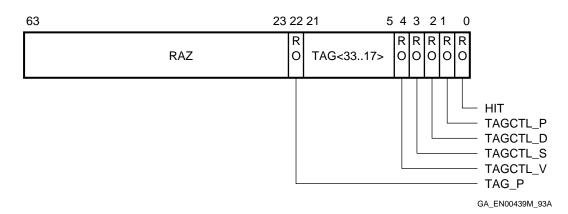

| 14–4  | BC_TAG Register Format           | 14–12 |

| 16–1  | Command Register Bits            | 16–19 |

| 16–2  | Mode Register Bits               | 16–21 |

| 16–3  | Extended Mode Register Bits      | 16–23 |

| 16–4  | Request Register                 | 16–26 |

| 16–5  | Write Single Mask Register       | 16–27 |

|       |                                  |       |

| 16–6  | Write All Mask Register                                       | 16–28 |

|-------|---------------------------------------------------------------|-------|

| 16–7  | DMA Controller Status Register                                | 16–29 |

| 16–8  | Set Chaining Mode Register                                    | 16–32 |

| 16–9  | Set Chaining Mode Register Status                             | 16–33 |

| 16–10 | Channel Interrupt Status Register                             | 16–34 |

| 16–11 | Chain Buffer Expiration Control Register                      | 16–35 |

| 16–12 | EISA Bus Master Status Latch                                  | 16–40 |

| 17–1  | Initialization Sequence                                       | 17–12 |

| 17–2  | ICW1                                                          | 17–14 |

| 17–3  | ICW2                                                          | 17–14 |

| 17–4  | ICW3 (Master Device)                                          | 17–15 |

| 17–5  | ICW3 (Slave Device)                                           | 17–15 |

| 17–6  | ICW4 021H (CNTRL-1) or 0A1H (CNTRL-2)                         | 17–16 |

| 17–7  | OCW1                                                          | 17–19 |

| 17–8  | OCW2                                                          | 17–20 |

| 17–9  | OCW3                                                          | 17–21 |

| 17–10 | Automatic Rotation                                            | 17–26 |

| 17–11 | Word Format for Polling Command I/O Read                      | 17–27 |

| 17–12 | ECLR Register Format                                          | 17–30 |

| 18–1  | NMI Status and Control Register                               | 18–5  |

| 18–2  | NMI Extended Status and Control Register                      | 18–7  |

| 18–3  | Port 0462 <sub>16</sub> Bit Map                               | 18–9  |

| 18–4  | Port 070 <sub>16</sub> Bit Map                                | 18–10 |

| 19–1  | Interval Timer Control Word Format                            | 19–7  |

| 19–2  | Interval Timer Counter Latch Command Format                   | 19–8  |

| 19–3  | Interval Timer Read Back Command Format                       | 19–9  |

| 19–4  | Interval Timer Status Byte Format                             | 19–10 |

| 20–1  | Line Control Register                                         | 20–5  |

| 20–2  | Line Status Register                                          | 20–8  |

| 20–3  | Modem Control Register                                        | 20–11 |

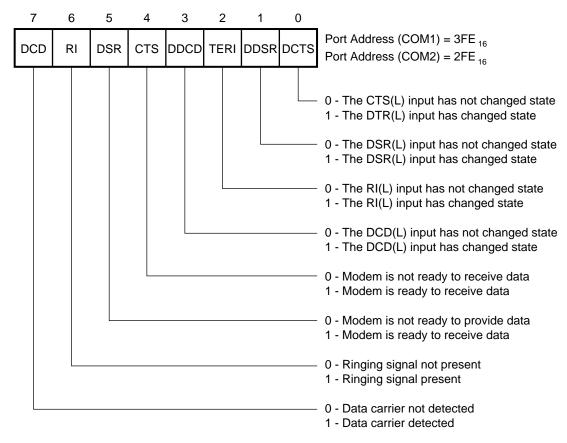

| 20–4  | Modem Status Register                                         | 20–14 |

| 20–5  | Interrupt Enable Register                                     | 20–20 |

| 23–1  | PS/2 Mode Register (Read Port $60_{16}$ After Writing Command |       |

|       | $20_{16}$ to Port $64_{16}$ )                                 | 23–5  |

| 23–2  | PS/2 Status Register (Read-Only—Port 64H)                     | 23–6  |

| B–1   | Internal Connector Locations                                  | B–2   |

| B–2   | EISA Connector Pin Numbers                                    | B–7   |

| B–3 | Keyboard and Mouse Connector | B–10 |

|-----|------------------------------|------|

| B–4 | Serial Port                  | B–11 |

| B–5 | Parallel Port                | B–12 |

#### Tables

| 1    | Bit Name Conventions                       | xxi   |

|------|--------------------------------------------|-------|

| 2–1  | Control Store Flags                        | 2–4   |

| 4–1  | SIMM Socket Configurations                 | 4–2   |

| 4–2  | Memory Address Generation                  | 4–4   |

| 6–1  | General Exception Isolation Matrix         | 6–3   |

| 6–2  | Machine Check Isolation Matrix             | 6–4   |

| 6–3  | Exception Priorities                       | 6–6   |

| 6–4  | DECchip 21064 CPU Interrupt Assignments    | 6–12  |

| 6–5  | Interrupt Priorities                       | 6–14  |

| 8–1  | System Address Map                         | 8–3   |

| 8–2  | EISA and H_BUS Byte Mask Generation        | 8–5   |

| 8–3  | L_BUS Address Map                          | 8–8   |

| 9–1  | NMI Error Types                            | 9–8   |

| 9–2  | Error Identification                       | 9–9   |

| 10–1 | Power-Up Sequence LED Codes                | 10–5  |

| 11–1 | Alpha AXP F-Floating Load Exponent Mapping | 11–7  |

| 11–2 | S_Floating Load Exponent Mapping           | 11–13 |

| 12–1 | ICCSR Register Fields                      | 12–9  |

| 12–2 | BHE and BPE Branch Prediction Selection    | 12–10 |

| 12–3 | Performance Counter 0 Input Selection      | 12–12 |

| 12–4 | Performance Counter 1 Input Selection      | 12–13 |

| 12–5 | EXC_SUM Register Fields                    | 12–17 |

| 12–6 | SL_CLR Register Fields                     | 12–18 |

| 12–7 | HIRR Register Fields                       | 12–23 |

| 13–1 | MM_CSR Register Fields                     | 13–7  |

| 13–2 | ABOX_CTL Register Fields                   | 13–8  |

| 13–3 | ALT_MODE Register Fields                   | 13–11 |

| 13–4 | BIU_CTL Register Fields                    | 13–13 |

| 13–5 | BC_SIZE Bits and Cache Sizes               | 13–18 |

| 13–6 | BC_PA_DIS Bits and Physical Addresses      | 13–18 |

| 13–7 | BIU_CTL Initialization Values              | 13–18 |

| BIU_STAT Register Fields                                 | 14–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Cache Status Register                               | 14–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Data Cache Status Error Modifiers                        | 14–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Processor Initiated Transactions                         | 15–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DMA Controller Address and Stop Register Correlation     | 16–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Address Shifting When Programmed for 16-Bit I/O Count by |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Words                                                    | 16–16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DMA Device Transfer Sizes                                | 16–25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Terminal Count and EOP Summary                           | 16–39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interrupt Controller I/O Address Map                     | 17–4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 82357 Interrupt Assignments                              | 17–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Content of Interrupt Vector Byte for 80x86 System Mode   | 17–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ICW1 Bit Definitions                                     | 17–13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ICW4 Bit Definitions                                     | 17–16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Initial Interrupt Controller Values                      | 17–17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reading Registers for Interrupt Controller Status        | 17–32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NMI Source Enable or Disable and Status Bits             | 18–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NMI Status and Control Register                          | 18–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NMI Extended Status and Control Register                 | 18–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 82357 (ISP) Stepping                                     | 18–8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Interval Timer and Counter-Timer I/O Address Map         | 19–2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |